CIRCUIT DESIGN EXAMPLES

2.1 Combinational Circuit Desion Example

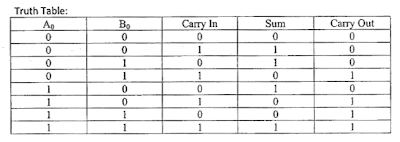

The circuit under study will be Full Adder, We will write a behavioral code of a t-bit

FA then write a structural code of a 4-bit FA.

Karnaugh Map:

"Sum" Map

"Carry Out" Map

2.1.2 Boolean Expressions of a 1-bit FA

2.1.3 VHDL Behavioral Code of 1-bit FA

library ieee;

use ieee.std_logic_1164.all;

-- definition of a full adder

entity fulladder is

port (a, b, ci: in std_logic;

sum, co: out std_logic);

end fulladder;

architecture fulladder_behav offulladder is

begin

sum <= (a xor b) xor ci ;

co <= (a and b) or (a and ci) or(b and ci);

end fulladder _behav;

2.1.4 VHDL Structural Code of 4-bit FA

library ieee;

use ieee.std_logic_1164.all;

entity FOURBITADD is

port (a, b: instd_logic_vector(3 downto 0);

Cin : in std_logic;

sum: out std_logic_vector (3 downto 0);

cout: out std_logic);

end FOURBITADD;

architecture STRUC of FOURBITADD is

signal c: std_logic_ vector (3 downto0);

component fulladder

port (a, b, c: in std_logic;

sum, carry: out std_logic);

end component;

begin

FA0: fulladder

port map (a(0), b(0), Cin, sum(0), c(1));

FA1: fulladder

port map (a(1), b(1), C(1), sum(1), c(2));

FA2: fulladder

port map (a(2), b(2), C(2), sum(2), c(3));

FA3: fulladder

port map (a(3), b(3), C(3), sum(3), cout);

VHDL Tutorial - LESSON 5